Ядро Linux 4.4

Документ содержит описание основных подсистем и драйверов ядра Linux, реализованных для поддержки аппаратуры СнК 1892ВМ14Я и модулей на базе СнК.

Ядро Linux поддерживает модули следующих ревизий:

Салют-ЭЛ24Д1 r1.3;

Салют-ЭЛ24Д1 r1.4;

Салют-ЭЛ24Д1 r1.5;

Салют-ЭЛ24Д1 r1.5 с установленным навигационным радиомодулем RF2Chan v2;

Салют-ЭЛ24Д2 r1.1;

Салют-ЭЛ24ОМ1 r1.1 с установленным Салют-ЭЛ24ПМ1 r1.1, r1.2;

Салют-ЭЛ24ОМ1 r1.2 с установленным Салют-ЭЛ24ПМ1 r1.2, Салют-ЭЛ24ПМ2 r1.0, r1.1, r1.2.

Файлы DTS *.dtsi, *.dts расположены в дереве исходных кодов U-Boot arch/arm/dts/*.dts*.

Пути до прочих файлов приведены относительно корня дерева исходных кодов Linux.

Подсистема управления тактовыми сигналами

Управление тактовыми сигналами и частотами в ядре Linux реализовано с использованием

Common Clock Framework.

Тактовые сигналы микросхемы описаны в виде дерева в файле mcom02.dtsi.

Для управления тактовыми сигналами и частотами используются следующие драйверы, описанные в

drivers/clk/elvees/clk-mcom.c:

mcom-clk-gate;mcom-clk-divider;mcom-clk-mux;mcom-clk-pll;mcom-cmctr.

Для корректного управления тактовыми сигналами каждый драйвер устройства, входящий в состав ядра Linux, должен реализовывать:

При инициализации драйвера:

Захват необходимого для устройства тактового сигнала, используя функцию

clk_get().Включение тактового сигнала, используя функцию

clk_enable().

При удалении драйвера:

Выключение тактового сигнала, используя функцию

clk_disable().

При инициализации подсистемы управления тактовыми сигналами происходит начальная настройка всех

PLL и делителей частот микросхемы. Устанавливаемые при инициализации значения множителей PLL и

делителей частот описаны в файле mcom02.dtsi.

Драйвер контроллера SPI dw_spi_mmio

Драйвер dw_spi_mmio управляет контроллерами SPI0 и SPI1 СнК 1892ВМ14Я.

Драйвер поддерживает следующие возможности:

Работа в режиме ведущего устройства.

Использование GPIO в качестве сигналов CS.

Настройка работы контроллера: фазы (CPHA) и полярности (CPOL) сигнала SCK, полярности сигнала CS (при использовании GPIO в качестве CS).

Поддержка слов длиной 8 и 16 бит.

Управление скоростью передачи в зависимости от ведомого устройства.

Ограничения драйвера:

Не поддерживается передача данных с помощью DMA.

Не поддерживается передача слов данных младшим битом вперед.

Драйвер контроллера PWM pwm-mcom

Драйвер pwm-mcom управляет контроллером PWM 1892ВМ14Я. Драйвер реализует стандартный интерфейс PWM

Файл с исходным кодом драйвера — drivers/pwm/pwm-mcom.c.

Описание DTS bindings представлено в файле

Documentation/devicetree/bindings/pwm/elvees,mcom-pwm.txt.

Ограничения драйвера:

Не реализовано управление каналами OUTB.

Не поддерживается режим счёта PWM-контроллера (PWM API не поддерживает данный режим).

Не реализовано управление предделителем.

Драйвер контроллера дисплея vpout-drm

Данный раздел применим к драйверу контроллера дисплея VPOUT СнК 1892ВМ14Я для подсистемы DRM — vpout-drm.

Документация, описывающая текущую версию подсистемы DRM, доступна по ссылке Linux GPU Driver Developer’s Guide.

Исходный код драйвера содержится в директории drivers/gpu/drm/vpout.

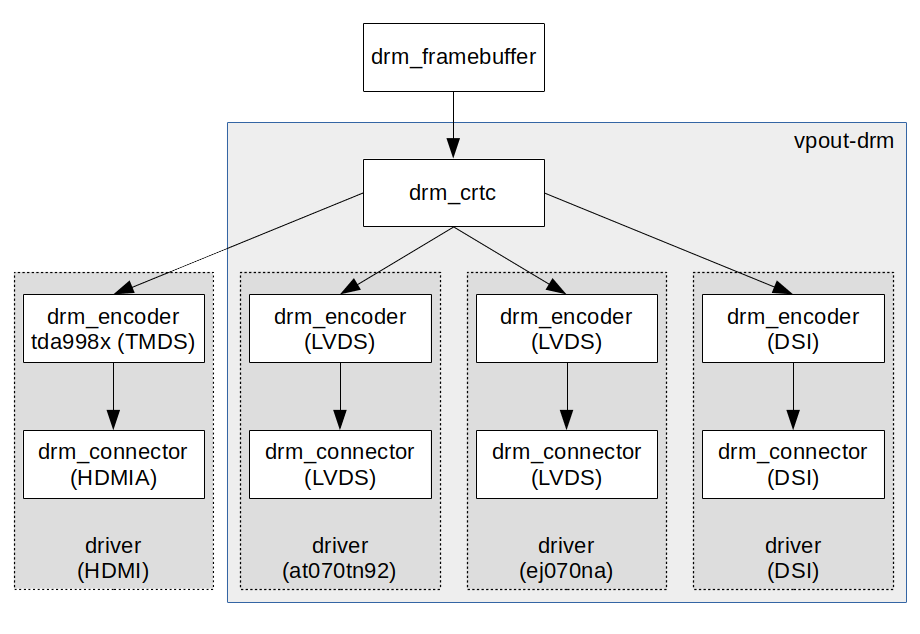

На рисунке Рис. 1 представлена диаграмма зависимостей компонентов драйвера Direct Rendering Manager (DRM).

Рис. 1 Диаграмма зависимостей компонентов драйвера DRM

Драйвер обеспечивает следующие возможности:

Разрешение экрана до 1920x1080 пикселей;

Поддержка внешнего HDMI передатчика NXP TDA998x;

Поддержка внешних панелей с заданием параметров дисплея через DTS;

Чтение Extended Display Identification Data (EDID);

Эмуляция фреймбуфера через устройство

/dev/fb0.

Ограничения драйвера:

Не поддерживаются чересстрочные видеорежимы (не поддерживаются контроллером дисплея VPOUT);

Не поддерживаются HDMI передатчики отличные от NXP TDA998x;

Не реализована поддержка абстракции плоскостей (plane abstraction);

Не поддерживается атомарная установка видеорежима.

Экспериментальные возможности драйвера, функционал не проверялся на аппаратуре:

Поддержка DSI-дисплеев:

Не поддерживается MIPI Display Command Set (MIPI DCS) и Extended Display Identification Data (EDID) DSI-дисплеев, т.к. MIPI DCS не поддерживается в аппаратуре;

Фиксированные параметры дисплея (разрешение, FPS) считываются из DTS. Дополнительно в командной строке ядра должно быть указано разрешение и тип DSI-дисплея;

В коде драйвера фиксировано количество DSI-линий — 4.

При использовании в качестве устройства вывода HDMI монитора драйвер устанавливает оптимальный для подключенного монитора видеорежим, определяемый по EDID. С помощью параметров ядра (kernel parameters) возможно установить фиксированный видеорежим. Например, следующая строка задает разрешение экрана в 1280×720 пикселей:

video=HDMI-A-1:1280x720

При использовании в качестве устройства вывода DSI-дисплея драйвер устанавливает видеорежим заданный с помощью параметров ядра (kernel parameters). При этом параметры дисплея считываются из DTS. Например, следующая строка задает разрешение экрана в 1280×720 пикселей:

video=DSI:1280x720

Подробное описание параметров ядра, задающих видеорежим, содержится в документе

Documentation/fb/modedb.txt.

Драйвер фреймбуфера vpoutfb

Для вывода на экран графического окружения на СнК используется подсистема

FBDev

и драйвер vpoutfb. Директория с исходным кодом драйвера — drivers/video/fbdev/vpoutfb.

Драйвер управляет контроллером VPOUT и HDMI-адаптером ITE IT66121.

Алгоритм работы драйвера:

Если в DTS в узле output присутствует свойство compatible=»ite,it66121», то выполнить настройку контроллера ITE IT66121, подключенного по I2C.

Считать из DTS видеорежим и настроить VPOUT для вывода в заданном видеорежиме.

Если в DTS отсутствует видеорежим или тайминги некорректны, или свойство output отсутствует, то настроить VPOUT для вывода в режиме 720p 60 FPS.

Вызов ioctl FBIOPUT_VSCREENINFO с заданием неподдерживаемого режима завершается с -EINVAL.

(Следовательно, вызов fbset завершится c ненулевым кодом возврата).

Поддерживаются следующие ioctl:

FBIOGET_VSCREENINFO;FBIOPUT_VSCREENINFO;FBIOGET_FSCREENINFO;FBIOGETCMAP;FBIOPUTCMAP;FBIOBLANK;VPOUTFB_GET_MEMORY_ID.

При появлении прерывания OUT_FIFO_INT блока VPOUT драйвер останавливает и переинициализирует VPOUT. При этом в dmesg печатается сообщение «Caught OUT_FIFO_INT, reinitializing VPOUT».

В драйвере не реализовано:

Чтение EDID HDMI-монитора и ограничение возможных разрешений согласно данным из EDID.

Остановка/запуск VPOUT при отключении/подключении HDMI-монитора.

Примечание

Т.к. автоматическое определение подключения HDMI-монитора отсутствует, драйвер может

быть выключен по умолчанию. Загрузка драйвера выполняется командой modprobe vpoutfb.

Примечание

Для управления видеорежимами может использоваться утилита fbset и файл fb.modes.

Драйвер считывает видеорежим из DTS в соответствии с описанием в

Documentation/devicetree/bindings/video/display-timing.txt.

В DTS-файле mcom02.dtsi описан формат цветовых компонентов

изображения, устанавливаемые при инициализации драйвера. Подробное описание полей узла устройства

VPOUT представлено в файле Documentation/devicetree/bindings/fb/vpoutfb.txt.

Примечание

Модуль vpoutfb используется консолью – перед выгрузкой модуля необходимо отключить консоль от драйвера:

echo 0 > /sys/class/vtconsole/vtcon1/bind

modprobe -r vpoutfb

Драйвер контроллера Ethernet arasan-gemac

Драйвер arasan-gemac управляет контроллером Ethernet Arasan GEMAC.

Драйвер реализует стандартный интерфейс network devices, описанный в

Documentation/networking/netdevices.txt.

Обработка RX-прерываний реализована с использованием интерфейса

NAPI.

Директория с исходным кодом драйвера — drivers/net/ethernet/arasan.

Драйвер поддерживает выполнение следующих операций из пространства пользователя:

Установка скорости (10/100/1000 Мб/с);

Установка дуплекса (full/half);

Установка уровня сообщений драйвера;

Установка MAC-адреса;

Чтение регистров контроллера Ethernet Arasan GEMAC утилитой ethtool;

Перезапуск автосогласования;

Проверка физического подключения;

Установка MTU кадра в диапазоне 68 – 3500 байт;

Отключение фильтрации пакетов (Promiscuous mode);

Включение приема всех multicast-пакетов (IFF_ALLMULTI);

Поддерживается фильтрация unicast-пакетов по MAC-адресу и multicast-пакетов по hash-таблице.

Примечание

Включение promiscuous mode повышает нагрузку на CPU.

Драйвер не поддерживает:

Управление паузой;

Чтение и запись EEPROM;

Wake-on-Lan;

Управление объединением прерываний.

Подсистема управления энергопотреблением

Подсистема управления энергопотреблением Linux определяет модели управления энергопотреблением (подробнее см. Device Power Management Basics):

System Sleep;

Runtime Power Management.

Модель System Sleep

В модели System Sleep определены состояния сна (подробнее см. System Power Management Sleep States):

Suspend-To-Idle (s2idle, freeze);

Standby, Power-On Suspend (shallow, standby);

Suspend-to-RAM (deep);

Suspend-to-disk (disk).

Поддерживаемые состояния сна:

Suspend-To-Idle;

Power-On Suspend.

Для энергосбережения в состоянии Power-On Suspend используются свойства драйверов:

поддержка приостановки (suspend) контроллера СнК в драйвере;

поддержка приостановки (suspend) контроллера внешнего интерфейса (приёмопередатчик CAN, Ethernet PHY, и т.д.) в драйвере;

поддержка CPU Hotplug (подробнее см. главу CPU Hotplug).

Поддержка приостановки реализована в драйверах контроллеров СнК:

avico (невозможен переход в Power-On Suspend во время сжатия);

delcore-30m;

designware-i2c;

designware-i2s;

dw-apb-gpio;

dw-apb-uart;

dw-wdt;

dwc2;

sdhci-mcom02.

Поддержка приостановки реализована в драйверах контроллеров внешних интерфейсов модулей на базе СнК:

bcm4329-fmac;

mcp2515;

ft313h.

Поддержка приостановки не реализована в драйверах контроллеров СнК:

arasan-gemac;

dw-apb-ssi;

dw-apb-timer;

mcom-pwm;

mfbsp-i2s;

nfc-v2p99;

pl330;

vinc;

vpout-drm;

vpoutfb.

Поддержка пробуждения (wakeup) реализована в драйверах:

dw-apb-uart (подробнее см. Пример пробуждения по событию от UART);

dw-apb-gpio;

rtc-ds1307 (подробнее см. Пример пробуждения по событию от RTC).

Пример пробуждения по событию от UART

Установить UART0 в качестве источника пробуждения:

echo enabled > /sys/devices/platform/38028000.serial/tty/ttyS0/power/wakeup

Перевести ОС в состояние сна:

echo freeze > /sys/power/state # enter Suspend-To-Idle state

или:

echo standby > /sys/power/state # enter Power-On Suspend state

В терминале на ПК отправить любой символ в приёмник контроллера UART0.

Пример пробуждения по событию от RTC

Перевести ОС в состояние сна до указанного времени пробуждения:

rtcwake -s 3 -m freeze # enter Suspend-To-Idle state

или:

rtcwake -s 3 -m standby # enter Power-On Suspend state

Модель Runtime Power Management

Для поддержки динамического управления энергопотреблением реализованы:

механизм CPU hotplug;

драйвер управления частотой ядер CPU cpufreq-dt.

Механизм CPU hotplug

Механизм CPU hotplug позволяет включать и выключать процессорные ядра, не перезагружая систему, что может использоваться:

для отключения CPU1;

для перехода системы в состояния сна.

Для выключения и включения процессорных ядер используются функции cpu_down() и cpu_up(),

описанные в файле kernel/cpu.c.

Использование через sysfs:

Для отключения питания ядра CPU1 необходимо выполнить:

echo 0 > /sys/devices/system/cpu/cpu1/online

Для включения питания ядра CPU1 необходимо выполнить:

echo 1 > /sys/devices/system/cpu/cpu1/online

Драйвер управления частотой ядер CPU cpufreq-dt

Штатный драйвер cpufreq-dt, позволяет управлять тактовой частотой ядер CPU0 и CPU1 через подсистему CPUfreq.

Директория с исходным кодом драйвера — drivers/cpufreq.

Список частот ядер CPU описан в DTS-файле mcom02.dtsi.

Описание DTS bindings представлено в файле

Documentation/devicetree/bindings/cpufreq/cpufreq-dt.txt.

Возможности драйвера:

Регуляторы масштабирования тактовой частоты ядер CPU (CPUfreq governors):

ondemand(по-умолчанию) — устанавливает тактовую частоту в зависимости от нагрузки на ядрах CPU;conservative— похож наondemand, но более экономный (предпочтение отдаётся меньшим тактовым частотам);performance— устанавливает тактовую частоту в максимальное значение;userspace— позволяет устанавливать частоту из пространства пользователя.

Управление регуляторами и частотами через

sysfs.

Ограничения драйвера:

Не поддерживается управление напряжением питания ядер CPU, т.к отсутствует поддержка в СнК.

Не поддерживается независимое управление частотой ядер CPU, т.к отсутствует поддержка в СнК.

Для установки тактовой частоты ядер из пространства пользователя необходимо:

Выбрать регулятор

userspace:echo userspace > /sys/devices/system/cpu/cpu0/cpufreq/scaling_governor

Выбрать частоту из поддерживаемых. Список частот доступен в файле

/sys/devices/system/cpu/cpu0/cpufreq/scaling_available_frequencies.Установить частоту. Значение частоты передаётся в кГц, например:

echo 312000 > /sys/devices/system/cpu/cpu0/cpufreq/scaling_setspeed

Подсистема UART в режиме RS-485

Для управления полудуплексными приёмопередатчиками RS-485 используются ioctl TIOCMBIS/TIOCMBIC:

int rts_flag = TIOCM_RTS;

ioctl(fd, TIOCMBIS, &rts_flag); // set send mode

ioctl(fd, TIOCMBIC, &rts_flag); // set receive mode

Примечание: модули Салют-ЭЛ24ОМ1 имеют полудуплексный приёмопередатчик RS-485.

Модуль dmatestcontig для тестирования SDMA

Модуль dmatestcontig не входит в состав исходных кодов Linux. Описание относится к модулю

dmatestcontig из коммита 4896f90a4cd335d91f5b9f2c1457f24baa7f98ce в репозитории модуля.

Модуль dmatestcontig основан на модуле

dmatest из коммита

9da2b1641a098eb9b00aacbfd7715efb6a503f7b в репозитории ядра Linux.

Модуль dmatestcontig позволяет провести тестирование SDMA с передачей данных, измерением производительности и проверкой правильности переданных данных. Управление SDMA осуществляется через DMA Engine API. Поддерживаемые типы передач: DMA_MEMCPY, DMA_XOR, DMA_PQ. Модуль поддерживает ряд параметров, которые позволяют задать размер буферов, количество повторений передач, максимальное число используемых каналов SDMA, количество потоков ядра, использующих канал SDMA, и др. Особенностью модуля dmatestcontig является то, что он позволяет выбрать типы передач, указывать специфические регионы памяти и включать частоты, которые, например, могут быть необходимы для обеспечения доступа к устройству памяти.

Модуль поддерживает все параметры, которые имеет модуль dmatest, а также добавляет параметры:

tests— типы выполняемых передач данных (по умолчанию выбраны все поддерживаемые типы передач);memregs— базовые адреса зарезервированных регионов памяти в DTS, в которые каналы SDMA должны адресовать запросы чтения/записи (по умолчанию регион выбирается автоматически);src— регионы памяти изmemregs, в которые каналы SDMA будут адресовать запросы чтения (по умолчанию первый регион, указанный вmemregs);dst— регионы памяти изmemregs, в которые каналы SDMA будут адресовать запросы записи (по умолчанию первый регион, указанный вmemregs);clocks— наименования узлов устройств в DTS, описывающих частоты, которых нужно включить, например, для обеспечения доступа SDMA к устройству памяти.

Параметр tests содержит битовую маску типов передач. Значение 1 бита включает тип передачи и

наоборот. Соответствие типов передач и номеров бит в параметре:

бит 0 — DMA_MEMCPY;

бит 1 — DMA_XOR;

бит 2 — DMA_PQ.

Резервирование регионов памяти в DTS выполняется согласно Reserved memory regions. Пример резервирования регионов памяти для модулей Салют-ЭЛ24ПМ:

reserved-memory {

#address-cells = <1>;

#size-cells = <1>;

ranges;

dmatestc_ddr0_reserved: dmatestc_ddr0@0x7f800000 {

no-map;

reg = <0x7f800000 0x800000>;

};

dmatestc_ddr1_reserved: dmatestc_ddr1@0xdf800000 {

no-map;

reg = <0xdf800000 0x800000>;

};

dmatestc_xyram_reserved: dmatestc_xyram@0x3a400000 {

no-map;

reg = <0x3a400000 0x40000>;

};

};

Элементы массивов src и dst ссылаются на регионы памяти по индексу региона в массиве

memregs. Номер канала SDMA, с которым ассоциируется регион, определяется индексом элемента в

src/dst.

Пример загрузки модуля с параметрами tests, src и dst:

modprobe dmatestcontig wait=1 run=1 noverify=1 tests=0x01 \

max_channels=5 memregs=0x7f800000,0xdf800000,0x3a400000 \

src=2,2,0,1,1 dst=0,0,2,2,1

modprobe -r dmatestcontig

В примере выше пять каналов SDMA адресуют запросы чтения/записи в регионы памяти следующим образом:

Канал 0: чтение из региона с базовым адресом 0x3a400000, запись в регион с адресом 0x7f800000.

Канал 1: чтение из региона с базовым адресом 0x3a400000, запись в регион с адресом 0x7f800000.

Канал 2: чтение из региона с базовым адресом 0x7f800000, запись в регион с адресом 0x3a400000.

Канал 3: чтение из региона с базовым адресом 0xdf800000, запись в регион с адресом 0x3a400000.

Канал 4: чтение из региона с базовым адресом 0xdf800000, запись в регион с адресом 0xdf800000.

Пример загрузки модуля с параметром clocks:

modprobe dmatestcontig run=1 noverify=1 memregs=0x7f800000,0x3a400000 \

src=0 dst=1 clocks="dsp_aclk"

modprobe -r dmatestcontig

В примере выше включается частота, описанная в узле устройства «dsp_aclk» в DTS, необходимая для обеспечения доступа к XYRAM.